# HP 3000 Simulator User's Guide 1-Jul-2023

#### **COPYRIGHT NOTICE**

The following copyright notice applies to the SIMH source, binary, and documentation:

Original code published 1993-2012, written by Robert M Supnik Copyright © 1993-2012, Robert M Supnik Copyright © 2012-2023, J. David Bryan

Permission is hereby granted, free of charge, to any person obtaining a copy of this software and associated documentation files (the "Software"), to deal in the Software without restriction, including without limitation the rights to use, copy, modify, merge, publish, distribute, sublicense, and/or sell copies of the Software, and to permit persons to whom the Software is furnished to do so, subject to the following conditions:

The above copyright notice and this permission notice shall be included in all copies or substantial portions of the Software.

THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE AUTHORS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE SOFTWARE.

Except as contained in this notice, the names of the authors shall not be used in advertising or otherwise to promote the sale, use, or other dealings in this Software without prior written authorization from the authors.

| 1 |      | Introduction                                                | 4   |

|---|------|-------------------------------------------------------------|-----|

|   | 1.1  | The HP 3000 Computer System                                 |     |

|   | 1.2  | Simulator Files                                             | 4   |

| 2 |      | Simulator Features                                          | 7   |

| 2 |      | Hardware-Equivalent Actions                                 |     |

|   | 2.1  | Simulator-Specific Commands                                 |     |

|   | 2.2  | 1                                                           |     |

|   | 2.2. |                                                             |     |

|   | 2.2. | J I J J                                                     |     |

|   |      | .2.3.1 EXAMINE, DEPOSIT, IEXAMINE, and IDEPOSIT             |     |

|   |      | .2.3.1 EXAMINE, DEPOSIT, TEXAMINE, and TDEPOSIT             |     |

|   |      | .2.3.3 RUN and GO                                           |     |

|   | 2.2. |                                                             |     |

|   | 2.2. |                                                             |     |

|   | 2.2. |                                                             |     |

|   | 2.2. | e e e e e e e e e e e e e e e e e e e                       |     |

|   | 2.2. |                                                             |     |

|   | 2.2. |                                                             |     |

|   |      | Realistic, Calibrated, and Optimized Timing                 |     |

|   | 2.3  | The Simulation Console and the System Console               |     |

|   | 2.4  | Tracing Simulator Operations                                |     |

|   | 2.5  |                                                             | 10  |

| 3 |      | Processor Device Simulations                                | 17  |

|   | 3.1  | Central Processing Unit                                     | 17  |

|   | 3.1. | 1 System Halt                                               | 18  |

|   | 3.1. | 2 Idling                                                    | 19  |

|   | 3.1. | 3 Simulation Stops                                          | 19  |

|   | 3.1. | 4 Tracing                                                   | 21  |

|   | 3.1. | 5 Registers                                                 | 24  |

|   | 3.2  | I/O Processor                                               | 24  |

|   | 3.3  | Selector Channel                                            | 26  |

|   | 3.4  | Multiplexer Channel                                         | 27  |

|   |      |                                                             | •   |

| 4 |      | Programmed I/O Device Simulations                           |     |

|   | 4.1  | 30032B Asynchronous Terminal Controller                     |     |

|   | 4.1. |                                                             |     |

|   | 4.1. |                                                             |     |

|   | 4.2  | 30033A Selector Channel Maintenance Board.                  |     |

|   | 4.3  | 30135A System Clock                                         | 36  |

| 5 |      | Selector Channel I/O Device Simulations                     | 38  |

| 5 | 5.1  | 30229B Disc Interface with Eight 7905/7906/7920/7925 Drives |     |

|   | 5.1. |                                                             |     |

|   | 5.1. |                                                             |     |

|   | 5.1. | 1                                                           |     |

|   | 5.1. |                                                             |     |

|   | J.1. |                                                             | • • |

| 5.1.5  | Tracing and Registers                                             | 42 |

|--------|-------------------------------------------------------------------|----|

| 6 M    | [ultiplexer Channel I/O Device Simulations                        | 44 |

| 6.1 30 | 0209A Line Printer Controller with One 2607/13/17/18 Line Printer |    |

| 6.1.1  | Device Options                                                    | 45 |

| 6.1.2  | Unit Options                                                      | 46 |

| 6.1.3  | Vertical Format Unit                                              | 47 |

| 6.1.4  | Tracing and Registers                                             |    |

| 6.2 30 | 0215A Tape Controller with Four 7970B/E Drives                    | 51 |

| 6.2.1  | Device Options                                                    |    |

| 6.2.2  | Unit Options                                                      | 53 |

| 6.2.3  | BOOT Command                                                      |    |

| 6.2.4  | Tracing and Registers                                             | 54 |

| 7 H    | P-IB Interface Module I/O Device Simulations                      |    |

| 7.1 30 | 0340A Intermodule Bus Adapter                                     | 56 |

| 7.2 30 | 0341A Channel Program Processor                                   | 58 |

| 7.3 31 | 262A General I/O Channel                                          | 59 |

| 7.3.1  | Device Options                                                    | 59 |

| 7.3.2  | Tracing and Registers                                             |    |

| 7.4 C  | S/80 Disc Drives                                                  |    |

| 7.4.1  | Configuration                                                     | 63 |

| 7.4.2  | Device Options                                                    | 64 |

| 7.4.3  | Unit Options                                                      |    |

| 7.4.4  | BOOT Command                                                      |    |

| 7.4.5  | Tracing and Registers                                             | 66 |

# **1** Introduction

This manual documents the features and operation of the HP 3000 simulator. It is intended for use in conjunction with the *SIMH Users' Guide* and *SIMH Users' Guide Supplement* manuals, which describe how to compile and run the simulator, as well as the general commands that may be entered at the Simulation Control Program (SCP) prompt.

This simulator is based on <u>SIMH</u> — the Computer History Simulator.

# 1.1 The HP 3000 Computer System

Hewlett-Packard sold the HP 3000 family of general-purpose business computers from 1972 through 2001. There are two major divisions within this family: the *classic* 16-bit, stack-oriented CISC machines, and the *Precision Architecture* 32-bit, register-oriented RISC machines that succeeded them. All machines run versions of MPE, the *Multiprogramming Executive* operating system.

Within the classic division, there are two additional subdivisions, based on the method used for peripheral connections: the original *SIO* machines, and the later *HP-IB* machines. The I/O interfacing hardware differs between the two types of machines, as do the privileged I/O machine instructions. The user instruction sets are identical, as are the register sets visible to the programmer. The I/O drivers are different to account for the hardware differences, and therefore they run slightly different versions of MPE.

This implementation is a simulator for the classic SIO machines. This group consists of the 3000 CX, the Series I, Series II, and the HP 3000 Series III that is simulated here. The CX and the Series I, which is a repackaged CX, are essentially subsets of the Series II/III — a smaller instruction set, limited memory size, and lower-precision floating-point instructions. Simulation of these machines may be added in the future. Future simulation of the HP-IB machines (the Series 30 through 70) is desirable, as the latest MPE versions run only on these machines, but documentation on the internals of the HP-IB hardware controllers is nonexistent.

The CX and Series I support 64K 16-bit words of memory. The Series II supports up to 256K, divided into four banks of 64K words each, and the Series III extends this to 1024K words using 16 banks. Memory is divided into variable-length code and data segments, with the latter containing a program's global data area and stack.

Memory protection is accomplished by checking program, data, and stack accesses against segment base and limit registers, which can be set only by MPE. Bounds violations cause automatic hardware traps to handler routines within MPE. Some violations may be permitted; for example, a Stack Overflow trap may cause MPE to allocate a larger stack and then restart the interrupted instruction. Memory references are position-independent, so moving segments to accommodate expansion requires only resetting of the segment registers to point at the new locations. Code segments are fully reentrant and shareable, and both code and data are virtual, as the hardware supports absent code and data segment traps.

The classic 3000s are stack machines. Most of the instructions operate on the value on the top of the stack (TOS) or on the TOS and the next-to-the-top of the stack (NOS). To improve execution speed, the 3000 has a set of hardware registers that are accessed as the first four locations at the top of the stack, while the remainder of the stack locations reside in main memory. A hardware register renamer provides fast stack pushes and pops without physically copying values between registers.

## 1.2 Simulator Files

The simulator sources are divided into a set of files for the Simulator Control Program and its support libraries, and a set of files for the HP 3000 device simulations; the latter reside in a subdirectory of the directory that contains the SCP files. The former set is common to all SIMH simulators, whereas the latter set is specific to the virtual machine being simulated. The files that make up this simulator are:

| Subdirectory | File               | Contains                                               |

|--------------|--------------------|--------------------------------------------------------|

| HP3000       | hp3000_cpu.h       | CPU architectural declarations                         |

|              | hp3000_cpu_fp.h    | Floating-point interface declarations                  |

|              | hp3000_cpu_ims.h   | CPU-to-IOP/channel interface declarations              |

|              | hp3000_defs.h      | System architectural declarations                      |

|              | hp3000_gic.h       | General I/O Channel architectural declarations         |

|              | hp3000_imb.h       | Intermodule Bus architectural declarations             |

|              | hp3000_io.h        | Device-to-IOP/channel interface declarations           |

|              | hp3000_mem.h       | Main memory subsystem interface declarations           |

|              | hp_disclib.h       | MAC/ICD disc controller simulator library declarations |

|              | hp_tapelib.h       | 797x tape controller simulator library declarations    |

|              | hp3000_atc.c       | Asynchronous Terminal Controller simulator             |

|              | hp3000_clk.c       | System Clock simulator                                 |

|              | hp3000_cpp.c       | Channel Program Processor simulator                    |

|              | hp3000_cpu.c       | CPU simulator                                          |

|              | hp3000_cpu_base.c  | CPU base instruction set simulator                     |

|              | hp3000_cpu_cis.c   | CPU COBOL II Extended Instruction Set simulator        |

|              | hp3000_cpu_eis.c   | CPU Extended Instruction Set simulator                 |

|              | hp3000_cpu_fp.c    | CPU floating point instruction set simulator           |

|              | hp3000_ds.c        | Cartridge Disc Interface simulator                     |

|              | hp3000_gic.c       | General I/O Channel simulator                          |

|              | hp3000_gic_dc.c    | CS/80 disc drive simulator                             |

|              | hp3000_imb.c       | Intermodule Bus simulator                              |

|              | hp3000_imba.c      | Intermodule Bus Adapter simulator                      |

|              | hp3000_iop.c       | I/O processor simulator                                |

|              | hp3000_lp.c        | Line Printer Interface simulator                       |

|              | hp3000_mem.c       | Main memory subsystem simulator                        |

|              | hp3000_mpx.c       | Multiplexer Channel simulator                          |

|              | hp3000_ms.c        | Magnetic Tape Controller Interface simulator           |

|              | hp3000_scmb.c      | Selector Channel Maintenance Board simulator           |

|              | hp3000_sel.c       | Selector Channel simulator                             |

|              | hp3000_sys.c       | SCP interface                                          |

|              | hp_disclib.c       | MAC/ICD disc controller simulator library              |

|              | hp_tapelib.c       | 797x tape controller simulator library                 |

| doc          | hp3000_guide.pdf   | HP 3000 Simulator User's Guide                         |

|              | hp3000_diag.txt    | SIMH/HP 3000 Diagnostics Performance Report            |

|              | hp3000_release.txt | HP 3000 Simulator Release Notes                        |

PDF files of the original HP 3000 hardware and software manuals are available from these repositories:

- Bitsavers

- The HP Computer Museum

The reference manuals used to develop the various simulated devices are listed in the comments at the start of the respective simulator source modules.

See the *Available Software* section of the release notes file for information on the availability of operating system software that runs on the simulator.

# 2 Simulator Features

| Device Name  | Simulates                                                          |

|--------------|--------------------------------------------------------------------|

| CPU          | 30003B Series III Computer with up to 1024 KW of memory            |

| IOP          | 30003B I/O Processor                                               |

| SEL          | 30030C Selector Channel                                            |

| ATCD         | 30032B Asynchronous Terminal Controller data interface             |

| ATCC         | 30032B Asynchronous Terminal Controller control interface          |

| SCMB1, SCMB2 | 30033A Selector Channel Maintenance Boards                         |

| MPX          | 30036B Multiplexer Channel                                         |

| CLK          | 30135A System Clock                                                |

| LP           | 30209A Line Printer Controller with one 2607/13/17/18 line printer |

| MS           | 30215A Magnetic Tape Controller with four 7970B/E drives           |

| DS           | 30229B Disc Interface with eight 7905/7906/7920/7925 drives        |

| IMBA         | 30340A Intermodule Bus Adapter                                     |

| СРР          | 30341A Channel Program Processor                                   |

| GIC          | 31262A General I/O Channel                                         |

| DC           | 31262A HP-IB connector with eight CS/80 disc units                 |

The HP 3000 simulator contains the following device simulations:

One instance of each listed device may be installed in the simulated computer chassis. Some devices support multiple connected units. As an example, the DS device simulates a single 30229B Disc Interface that connects up to eight drives. However, a second 30229B connecting an additional eight drives is not supported.

Certain devices support the creation of more than one instance; these are noted in their respective individual device descriptions below. For example, the GIC device supports the creation of up to 14 separate instances, representing the installation of 14 GIC Printed Circuit Assemblies in the computer chassis. Each GIC instance is a separate device, and all GICs may be used concurrently.

The simulator has been tested with and supports the following operating systems:

• MPE V/R version E.01.00.

In addition, the simulator generally passes the HP 32230 Stand-Alone Diagnostics suite; see *hp3000\_diag.txt* for details.

The simulator may be configured to stop for any of these conditions:

- Attempted execution of an instruction that enters an infinite loop (e.g., BR P+0).

- Attempted execution of a PAUS instruction.

- Attempted execution of an undefined instruction.

- Attempted execution of an unimplemented instruction.

MPE normally handles these conditions internally. However, when running diagnostics, it may be helpful to set one or more of these stop conditions. In particular, some diagnostics execute a PAUS instruction to wait for operator action, rather than external interrupts, or branch in an infinite loop to indicate an error condition. Unless the corresponding simulator stops are active, no indications of these conditions will be observed.

The simulator also provides extensive facilities for tracing CPU and I/O device operations.

# 2.1 Hardware-Equivalent Actions

The current implementation does not provide simulations of the CPU or peripheral device front panels. Instead, commands entered through the simulation console are used to perform hardware actions. The simulation commands that substitute for CPU front-panel actions are:

| Hardware Front-Panel Action                 | Equivalent Simulation Command |

|---------------------------------------------|-------------------------------|

| Pressing the RUN/HALT button while halted   | RUN                           |

| Pressing the RUN/HALT button while running  | CTRL+E CTRL+E                 |

| Pressing the LOAD and ENABLE buttons        | LOAD                          |

| Pressing the DUMP and ENABLE buttons        | DUMP                          |

| Toggling the CPU RESET switch               | RESET                         |

| Setting the PF/ARS switch to ENABLE         | SET CPU ARS                   |

| Setting the PF/ARS switch to DISABLE        | SET CPU NOARS                 |

| Displaying the Current Instruction Register | EXAMINE CIR                   |

| Displaying the System Switch Register       | EXAMINE SWCH                  |

| Setting the System Switch Register          | DEPOSIT SWCH <value></value>  |

Mounting media on a peripheral device is simulated by the *ATTACH* command. For example, entering the *ATTACH LP <printer-image-filename>* command is equivalent to loading paper into an HP 2617A Line Printer. Inserting a disc pack into an HP 7905A disc drive set for unit 2 is simulated by the *ATTACH DS2 <disc-image-filename>* command.

Each of these commands is explained in more detail below.

In hardware, loading programs into memory from a device is accomplished by setting the System Switch Register to the desired control and device number and pressing the LOAD and ENABLE buttons together to initiate the cold load sequence. In simulation, a cold load may be performed either explicitly or implicitly. Explicit operation is described in the *LOAD, DUMP, and BOOT* section below. As a convenience, **BOOT** <**device** > commands may be used to implicitly cold load their respective devices and are described in the individual device descriptions below.

# 2.2 Simulator-Specific Commands

In general, all of the commands documented in the *SIMH Users' Guide* manual are available for use with the HP 3000 simulator. Commands whose execution or parameters are implementation-defined are specified below.

#### 2.2.1 Numeric Display and Entry

When examining or depositing into memory, the radix for addresses is octal, and the default radix for numeric data is octal. The data default may be changed for a specific device with the *SET <device> <radix>* command, or the radix may be overridden temporarily with a command line switch, as follows:

| SET <radix><br/>Option</radix> | Command<br>Switch | Data Interpretation |

|--------------------------------|-------------------|---------------------|

| BINARY                         | –B                | Binary values       |

| OCTAL                          | -0                | Octal values        |

| DECIMAL                        | –D                | Decimal values      |

| HEX                            | –H                | Hexadecimal values  |

When examining or depositing into device registers, the default radix for the specified register is used unless overridden with one of the above command line switches. Defaults are listed in the register table associated with each device.

When examining or depositing into attached device files, the radix for addresses is decimal, and the default radix for numeric data is octal. The data default may be changed with the *SET <device> <radix>* command, or the radix may be overridden temporarily with one of the above command line switches.

# 2.2.2 Symbolic Display and Entry

When examining or depositing into memory, certain registers, or attached device files, command line switches specifying the symbolic mode and format may be used to override the default numeric mode, as follows:

| Switch     | Mode Interpretation                                                     |  |

|------------|-------------------------------------------------------------------------|--|

| -A         | A single character in the right-hand byte                               |  |

| -C         | A two-character packed string                                           |  |

| –Е         | E An EDIT subprogram operation mnemonic                                 |  |

| –ER        | An EDIT subprogram operation mnemonic starting with the right-hand byte |  |

| <b>–</b> I | An I/O program instruction mnemonic                                     |  |

| –L         | A channel program instruction mnemonic                                  |  |

| -M         | A CPU instruction mnemonic                                              |  |

| -Т         | A CPU status mnemonic                                                   |  |

In addition, certain 8-bit devices allow pairs of successive bytes in their attached device files to be interpreted as 16-bit words. These devices normally display or enter values as bytes but can be overridden to work with words by including one the following mode switches:

| Switch | Switch Mode Interpretation    |  |

|--------|-------------------------------|--|

| -C     | A two-character packed string |  |

| —M     | A CPU instruction mnemonic    |  |

| —W     | A 16-bit numeric value        |  |

In the absence of a mode switch, entering values with a leading ' (apostrophe) implies -A, and a leading ' (quotation mark) implies -C. The specific registers supporting symbolic mode are indicated in their respective device sections below.

If the -C switch is specified, the value is displayed as two characters separated by a comma. Alphanumeric, punctuation, and symbol characters are displayed within apostrophes, control characters are displayed as ASCII name abbreviations, and characters above 128 decimal are displayed in escaped numeric form with a leading backslash followed by an octal number. Depositing with -C accepts two displayable characters. If a single character is supplied, the low byte of the resulting value will be zero; follow the character with a space to pad the low byte with a blank.

If the -M switch is specified, the value is displayed as a CPU machine instruction mnemonic if it is defined. If it is not, it is displayed as a numeric value in the CPU's data radix. Any numeric operands present are displayed in a default radix unless overridden by the addition of one of these mutually exclusive format switches:

| Switch Format Interpretation |                                           |  |

|------------------------------|-------------------------------------------|--|

| -A                           | A single character in the right-hand byte |  |

| -B A binary value            |                                           |  |

| -0                           | An octal value                            |  |

| -D                           | A decimal value                           |  |

| -H                           | A hexadecimal value                       |  |

Numeric operands are displayed in a radix suitable to the type of the value. For CPU instruction operands:

- Register-relative displacements, S-register decrements, and K fields are displayed in the CPU's address radix, which is octal.

- Shift counts, bit positions, and starting bits and counts are displayed in decimal unless overridden by a switch on the command line.

- CIR values for the PAUS and HALT instructions are displayed in octal unless overridden by a switch on the command line.

- Immediate values are displayed in the CPU's data radix, which defaults to octal but may be set to a different radix or overridden by a switch on the command line.

For I/O and channel program instruction operands:

- Address values are displayed in the CPU's address radix, which is octal.

- Counts are displayed in decimal unless overridden by a switch on the command line.

- Control and status values are displayed in the CPU's data radix, which defaults to octal but may be set to a different radix or overridden by a switch on the command line.

For CPU status values:

• The current code segment number is displayed in the CPU's data radix, which defaults to octal but may be set to a different radix or overridden by a switch on the command line.

For EDIT subprogram operands:

- Branch displacement fields are displayed in the CPU's address radix, which is octal.

- Character counts, loop counts, and source and target adjustments are displayed in decimal unless overridden by a switch on the command line.

- Invalid operation codes are displayed in the CPU's data radix, which defaults to octal but may be set to a different radix or overridden by a switch on the command line.

Each EDIT subprogram operation occupies from 1 to 257 bytes in memory. If a multi-byte operation begins within the examined memory range, the additional bytes required to complete the operation are displayed. Including the – R switch will begin decoding with the right-hand (low-order) byte of the first memory word in the range rather than with the left-hand byte. Invalid extended operation codes are displayed as a comma-separated pair of half-byte values (e.g., "17,12").

If the indicated display radix is not the same as the current CPU data radix, a leading character @, %, #, or !, is printed for binary, octal, decimal, or hexadecimal numbers, respectively.

When the simulator examines the bit patterns of instructions in memory or registers to display in mnemonic form, each will fall into one of four categories:

- 1. Defined (canonical) instruction encodings, where all bits are defined or all reserved bits are zero (e.g., LOAD).

- 2. Undefined (non-canonical) instruction encodings, where reserved fields are "don't care" bits (e.g., MOVE).

- 3. Undefined (non-canonical) instruction encodings, where reserved fields are decoded (e.g., IXIT).

- 4. Unimplemented instruction encodings (e.g., stack opcode 072, or EADD without the EIS firmware option installed).

The names of the canonical instructions in category 1 are displayed in uppercase, as are the names of the noncanonical instructions in category 2. The non-canonical instruction names in category 3 are displayed in lowercase. This is to indicate to the user that the instructions that will be executed may not be the ones expected from the decoding. Instruction names in category 4 that correspond to supported firmware options are displayed in uppercase, regardless of whether or not the option is enabled. Category 4 encodings that do not correspond to instructions are displayed in octal.

#### 2.2.3 Memory Addressing

The CPU simulator supports two forms of memory addresses:

- An absolute address consisting of a 2- or 4-bit bank number and a 16-bit offset within the bank, separated by a period (e.g., **17.177777**).

- A relative address consisting of a 16-bit offset within a bank specified by a bank register (e.g., 177777).

Command line switches modify the interpretation of relative addresses as follows:

| Switch    | Interpretation                                 |  |

|-----------|------------------------------------------------|--|

| -P        | The implied bank number is obtained from PBANK |  |

| <b>_S</b> | The implied bank number is obtained from SBANK |  |

If no switch is specified, the implied bank number is obtained from DBANK.

#### 2.2.3.1 EXAMINE, DEPOSIT, IEXAMINE, and IDEPOSIT

The following CPU memory address forms are valid:

```

EXAMINE <bank>.<offset>

EXAMINE <dbank-offset>

EXAMINE -P <pbank-offset>

EXAMINE -S <sbank-offset>

```

Addresses are always displayed in *<bank>.<offset>* form.

#### 2.2.3.2 BREAK and NOBREAK

The following address forms are valid:

```

BREAK

BREAK <bank>.<offset>

BREAK <pbank-offset>

```

The address defaults to the current values of PBANK and/or P. All breakpoint addresses are stored and displayed in *<bank>.<offset>* form.

#### 2.2.3.3 RUN and GO

The following address form is valid:

RUN <pbank-offset>

The offset is stored in P. If P does not lie within the PB-to-PL range, the command will be rejected.

The SIMH *RUN* command typically resets all devices before beginning execution. For the HP 3000, CPU and I/O resets are performed at the start of the cold load sequence; a reset after the cold load sequence completes will destroy the Interrupt Control Stack register setup performed by the microcode. Therefore, in this simulator, the *RUN* and *GO* commands are equivalent; neither resets the devices. If an explicit CPU reset is desired, the *RESET CPU* command may be used.

#### 2.2.4 LOAD, DUMP, and BOOT

The *LOAD* command implements the 3000 cold load facility. It is equivalent to pressing the LOAD and ENABLE buttons on the hardware front panel. The syntax is:

```

LOAD {<control/devno>}

```

The SWCH register controls the cold load sequence; the upper byte contains a device-specific control value, and the lower byte contains the device number. If the optional control/device number value is supplied, it is deposited into the SWCH register before initiating the cold load sequence. Otherwise, the SWCH register value must be set before entering the command. In either case, the device number must be between 3 and 63 for an SIO device, or 125 for an HP-IB device, or the command will not complete.

The **DUMP** command implements the 3000 cold dump facility. It is equivalent to pressing the DUMP and ENABLE buttons on the hardware front panel. The syntax is:

DUMP {<control/devno>}

The CPU *DUMPCTL* and *DUMPDEV* settings control the cold dump sequence and correspond to the settings of the jumper blocks on the rear of the CPU front panel. If the optional control/device number value is supplied, it is deposited into the SWCH register before initiating the cold dump sequence. Otherwise, the *DUMPCTL* and *DUMPDEV* values are deposited into the SWCH register. A successful cold dump sets the CIR register to the number of 64K memory banks dumped. For example, dumping a 512K-word system will display Cold dump complete, CIR: 000010 if the operation succeeds.

The control/device number values are entered in the current CPU data radix. Before entering either command, unit 0 of the associated device must be attached. A failed cold load will cause a system halt. A failed cold dump will set the CIR register to the memory bank number at which the operation failed; if the dump device is not ready or not write-enabled, the CIR register will be set to zero.

Bootable peripherals, such as the tape and disc drives, also implement the **BOOT** command. Entering a **BOOT** command for one of these devices will preset the SWCH register to the appropriate value before executing a cold load. Cold load supports booting only from unit 0 of the target device.

#### 2.2.5 POWER FAIL and POWER RESTORE

The **POWER FAIL** command (and its alternate forms **POWER OFF** and **POWER DOWN**) simulates removing AC power from the system. If the CPU was executing when the command is entered, a power-fail interrupt is generated, and MPE initiates its power-fail processing that ends with a programmed HALT. Otherwise, power is removed, and the CPU remains halted. **POWER FAIL** is accepted only when power is on.

The **POWER RESTORE** command (and its alternate forms **POWER ON** and **POWER UP**) simulates restoring AC power to the system; it is accepted only when power is off. If the CPU was executing when power failed, a power-on trap is generated, and, if auto-restart is enabled, MPE initiates its power-recovery processing. If auto-restart is disabled, the trap is set up but the simulator must be resumed with a **CONTINUE** command to execute the trap. If the CPU was halted when power failed, power is restored, and the CPU remains halted. Once power is off, the **CONTINUE**, **STEP**, **GO**, and **RUN** commands will not be accepted until power is restored.

### 2.2.6 Device Configuration

Most devices support user configuration. The general forms of the configuration commands are:

```

SET {<switch> ...} <device> <option> {,<option> ...}

SET {<switch> ...} <unit> <option> {,<option> ...}

```

The options available and applicable switches are described in the individual device descriptions below.

#### 2.2.7 Enabling and Disabling Devices

All devices other than the processor devices may be disabled or enabled. Disabling a device simulates removing the associated interface from the system cabinet. To disable or enable a device, use:

| Command                        | Action             |

|--------------------------------|--------------------|

| SET <device> DISABLED</device> | Disable the device |

| SET <device> ENABLED</device>  | Enable the device  |

Devices that consist of multiple addressable units connected to a controller allow the units to be individually disabled or enabled. Disabling simulates disconnecting the associated unit from the controller. The commands to disable or enable a unit are:

| Command                    | Action           |

|----------------------------|------------------|

| SET <unit> DISABLED</unit> | Disable the unit |

| SET <unit> ENABLED</unit>  | Enable the unit  |

Each of the above command options is replicated in the option tables of the devices to which they apply.

#### 2.2.8 I/O Interface Assignments

HP 3000 hardware I/O interfaces have configuration jumpers that set device numbers, interrupt masks, and Multiplexer Channel service request priority numbers. In addition, the interrupt poll order, and therefore the interrupt priority, is established by the position of each interface along the daisy-chained interrupt cable.

Device options that may be specified to change or display interface configurations are:

| Option             | Valid Values                          | Action                 |  |

|--------------------|---------------------------------------|------------------------|--|

| DEVNO              | 0-127                                 | Set the device number  |  |

| INTMASK 0-15, D, E |                                       | Set the interrupt mask |  |

| INTPRI             | 0-31 Set the interrupt priority       |                        |  |

| SRNO               | SRNO 0-15 Set the service request num |                        |  |

For example:

```

SET MS DEVNO=6

SET MS INTMASK=E

SHOW MS DEVNO,INTMASK

```

The interrupt mask may be set to a numeric value, to D to disable the mask always, or to E to enable the mask always. Numeric mask values may be shared among devices. However, if two device, interrupt priority, or service request priority numbers conflict, the simulator will report the error when execution is attempted.

The default settings are:

| Device<br>Name | Device<br>Number | Interrupt<br>Priority | Interrupt<br>Mask | Service<br>Request<br>Number |

|----------------|------------------|-----------------------|-------------------|------------------------------|

| CPU            | _                | -                     | _                 | -                            |

| IOP            | _                | -                     | _                 | -                            |

| SEL            | _                | _                     | —                 | _                            |

| MPX            | 127              | _                     | —                 | _                            |

| ATCD           | 7                | 0 E                   |                   | -                            |

| ATCC           | 8                | 8                     | E                 | _                            |

| CLK            | 3                | 1 –                   |                   | _                            |

| DS             | 4                | 4 4 E                 |                   | -                            |

| LP             | 14               | 18                    | E                 | 11                           |

| MS             | 6                | 14                    | E                 | 3                            |

| SCMB1          | 65 10            |                       | _                 | 0                            |

| SCMB2          | 66               | 11 –                  |                   | 1                            |

| IMBA           | 125              | 12                    | 12 – –            |                              |

The SCMB device numbers and interrupt priorities may be set to any unused values. The device numbers of the MPX and IMBA devices cannot be changed.

## 2.2.9 SAVE and RESTORE

**SAVE** and **RESTORE** are supported only when the simulator executable used to restore the simulator state file is the same simulator executable used to save the file. Correctly restoring the state of the simulator depends on the layout of internal structure variables being identical to the layout of the structure variables that were saved. This is guaranteed only when using the same executable, as the layout used is implementation-defined.

# 2.3 Realistic, Calibrated, and Optimized Timing

Devices simulate their I/O operation delays (disc seeks, magnetic tape reads, printer paper movements, etc.) by counting specified numbers of "event ticks." For example, a disc seek completion might be scheduled to occur 500 event ticks after command initiation. Generally, one event tick is counted for each machine instruction executed, although some complex instructions may count an event tick for each internal step of the instruction (e.g., for each word moved within a block-move instruction). Device simulations provide commands that determine how the appropriate tick counts are selected for I/O operations timing:

| Command                        | Action                                        |

|--------------------------------|-----------------------------------------------|

| SET <device> REALTIME</device> | Configure the device to use realistic timing  |

| SET <device> CALTIME</device>  | Configure the device to use calibrated timing |

| SET <device> FASTTIME</device> | Configure the device to use optimized timing  |

A device configured to use *realistic timing* selects its tick counts to encompass the same number of machine instructions as would be executed in hardware. In real-time mode, an operation taking ten milliseconds in hardware will complete after 4000 machine instructions are executed, based on an average instruction execution time of 2.5 microseconds. In this mode, a software program will execute approximately the same number of instructions during a device operation that it would do on a real machine. Host machine speed and execution of concurrent host programs will not affect the number of simulated instructions executed for a given operation.

A device configured to use *calibrated timing* selects its tick counts to align the simulated operation periods with the corresponding time periods on the host system. In calibrated-time mode, an operation taking ten milliseconds in hardware will complete after ten milliseconds has elapsed on the host system. Because the simulator is generally one or two orders of magnitude faster than the hardware, a software program will execute far more code during a device operation than it would do on a real machine. In this mode, the amount of code that executes will vary with the speed of the host machine and the load placed on that machine by other concurrent processes, as the simulator continually adjusts the tick counts up and down to maintain synchronization with the host time.

A device configured to use *optimized timing* selects its tick counts to minimize the operation delays. In fast-time mode, an operation taking ten milliseconds in hardware will complete after the minimum amount of time acceptable to the executing software has elapsed. In this mode, device operations complete far more quickly than they do in hardware. There are limits, however, to how fast I/O operations may occur without causing software malfunctions. In practice, system software often contains assumptions regarding the time certain operations take, so event timing may not be arbitrarily reduced. For instance, an I/O driver may "know" that a line printer takes 50 milliseconds to print a line, and therefore it can ignore interrupts safely for several milliseconds after initiating the print cycle. If the printing time is reduced below that threshold, the driver may fail to operate correctly. The default optimized-timing settings have been empirically determined to work with the supported operating systems listed above, and each device simulator allows the user to modify those settings via registers if needed.

To illustrate how the modes affect timing, consider a simulation of a Teletype terminal that operates at 10 characters per second. If the simulator runs 15 times faster than a real machine, then a user would observe that printing 100 characters takes:

- 10 seconds in CALTIME mode (100 characters × *n* event ticks per character adjusted to take exactly 100 mS each on the host system)

- 667 milliseconds in REALTIME mode (100 characters × 40,000 event ticks per character × 2.5 µS per tick ÷ 15 times hardware speed)

- 8.33 milliseconds in FASTTIME mode

(100 characters × 500 event ticks per character × 2.5 µS per tick ÷ 15 times hardware speed)

If the SCP **SET THROTTLE** command is used to reduce the speed of the simulator, CALTIME operations will not be affected, but REALTIME and FASTTIME operations will slow proportionally. Reducing simulator speed to that of the original hardware will cause REALTIME operation times to equal CALTIME times.

Devices offer only those modes that are generally useful. For example, the CPU process clock and system clock may be configured to use REALTIME or CALTIME modes. The real-time mode will satisfy the expectations of hardware diagnostics that check the timing of operations via delay loops, whereas the calibrated mode will update the MPE time-of-day clock as expected by users of the simulated system. FASTTIME mode is not offered, as it makes no sense to ignore the programmed time period settings and use a fixed arbitrary period instead.

Devices performing input or output typically offer a REALTIME mode for use when running the diagnostics and a FASTTIME mode for use when running operating systems. In general, software running under simulation will run faster when devices are configured for optimized-time mode, and this is the default for all peripheral devices.

# 2.4 The Simulation Console and the System Console

When the simulator is started, the SCP command prompt appears at the *simulation console*. For windowed host operating systems, this is typically the same window from which the simulator was started. Once an execution command such as *RUN* is entered at the simulation console, the standalone diagnostics and MPE operating system begin their user interactions at the *system console*. The HP 3000 reserves channel 0 of the ATC terminal multiplexer for the system console.

For convenience and by default, the system console is initially connected to the simulation console, so that SCP and MPE operator commands may be entered from the same window. Additional *user terminals* may be connected via Telnet or serial ports to ATC channels 1-15 as described later.

The system console may be separated from the simulation console by using the SET CONSOLE TELNET=<port> or SET CONSOLE SERIAL=<port> command. This leaves the simulation console at the initiating window and moves the system console to a Telnet or serial port, allowing the use of an HP terminal or terminal emulator. Entering the SET CONSOLE NOTELNET or SET CONSOLE NOSERIAL command will rejoin the consoles

# 2.5 Tracing Simulator Operations

The simulator provides options for extensive tracing of the internal operations of all devices. This is useful as an aid to hardware and software debugging as well as to gain an understanding of the internal operations of the simulated devices. Each device offers multiple trace reporting levels, from command overviews to detailed backplane signal assertions. Tracing for each device and its separate reporting levels may be enabled independently.

To obtain a trace, two SCP commands must be given. First, a *debug log* must be established with the **SET DEBUG <target>** command. This command is described in detail in the "Controlling Debugging" section of the *SIMH Users' Guide* manual. Typically, the target is a text file, so that the trace may be reviewed after capture. Second, tracing must be enabled for the desired devices with **SET <device> DEBUG=<option>** commands. These are documented below in the sections that refer to the simulated devices.

The reporting level options table given for each device is arranged in order of increasing detail. The first option listed provides the broadest overview with the least specific detail and generates the smallest number of trace lines, thereby slowing program execution the least. Subsequent options provide increasing detail at the expense of larger debug log files. Enabling all trace options with a *SET <device> DEBUG* command provides the fullest picture of device operation but may generate very large log files.

Some options enable tracing of periodic events, e.g., a clock tick or a device poll. Use caution when specifying these options, as the trace log may fill rapidly. Options that trace periodic behavior are noted in the option descriptions.

The formats of the trace output are specific to the devices being traced. Examples are provided in each device description section below.

# **3** Processor Device Simulations

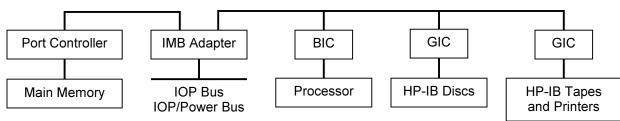

The HP 3000 computer consists of the following subsystems:

- 30003B Central Processing Unit

- 30003B I/O Processor

- 30030C Selector Channel

- 30036B Multiplexer Channel

#### 3.1 Central Processing Unit

The HP 3000 Central Processing Unit contains the microprogrammed machine instruction execution unit, main memory, and process clock. CPU options specify the memory size, installed firmware, and simulation configuration. The CPU is configured with commands of the form:

SET {-F} CPU <option>

Device options that may be specified are:

| Option                                | Action                                                          |

|---------------------------------------|-----------------------------------------------------------------|

| 128K                                  | Set the memory size to 128K words                               |

| 256K                                  | Set the memory size to 256K words                               |

| 384K                                  | Set the memory size to 384K words                               |

| 512K                                  | Set the memory size to 512K words                               |

| 768K                                  | Set the memory size to 768K words                               |

| 1024K                                 | Set the memory size to 1024K words; default for Series III      |

| EIS                                   | Enable the Extended Instruction Set firmware; default           |

| NOEIS                                 | Disable the Extended Instruction Set firmware                   |

| CIS                                   | Enable the COBOL II Extended Instruction Set firmware           |

| NOCIS                                 | Disable the COBOL II Extended Instruction Set firmware; default |

| ARS                                   | Enable auto-restart after a power failure; default              |

| NOARS                                 | Disable auto-restart after a power failure                      |

| CALTIME                               | Use calibrated process clock timing; default                    |

| REALTIME                              | Use realistic process clock timing                              |

| IDLE                                  | Enable idle detection                                           |

| NOIDLE                                | Disable idle detection; default                                 |

| DUMPDEV= <n></n>                      | Set the dump device number; default is 6                        |

| DUMPCTL= <n></n>                      | Set the dump device control value; default is 004               |

| STOP= <option></option>               | Enable simulation stops                                         |

| NOSTOP                                | Disable simulation stops; default                               |

| EXEC= <match>[;<mask>]</mask></match> | Enable execution tracing of matching instructions               |

| NOEXEC                                | Disable execution tracing; default                              |

| DEBUG= <option></option>              | Enable tracing                                                  |

| NODEBUG                               | Disable tracing; default                                        |

The initial configuration is a Series III system with 1024K words of memory. If the memory size is being reduced, and the memory being truncated contains non-zero data, the simulator asks for confirmation before proceeding.

The confirmation request may be suppressed by using the -F (force) switch. Data in the truncated portion of memory is lost.

The **SET CPU EIS** command simulates the installation of the HP 30012A Extended Instruction Set firmware on the ROM PCA and removal of the W1 and W8 jumpers from the CIR PCA to enable decoding of the instructions. The set includes four-word extended-precision floating-point instructions and decimal arithmetic instructions. The EIS is standard on HP 3000 Series II and III machines, so this option is enabled by default. If the set is disabled with the **SET CPU NOEIS** command, MPE will emulate the instructions in software.

The **SET CPU CIS** command simulates the installation of the HP 32234A COBOL II Extended Instruction Set firmware on the ROM PCA and removal of the W4 jumper from the CIR PCA to enable decoding of the instructions. The HP 32233A COBOLII/3000 compiler and programs produced by this compiler require the firmware to execute. If it is not installed, these programs will abort at run time with *ILLEGAL INSTRUCTION* errors.

The position of the PF/ARS switch on the back of the system control panel determines how the CPU responds to AC power returning after a power failure. In the *enable* position, simulated by the *SET CPU ARS* command, power restoration will initiate an automatic restart of the operating system. In the *disable* position, simulated by the *SET CPU ARS* command, power *CPU NOARS* command, power restoration will set up the system for a restart, which must be performed manually by entering a *CONTINUE*, *STEP*, *GO*, or *RUN* command.

Calibrated timing adjusts the process clock to match actual elapsed time. Realistic timing bases the process-clock interval on machine instructions executed.

When enabled by a *SET CPU IDLE* command, execution of a PAUS instruction will idle the simulator. While idle, the simulator does not use any host system processor time. Idle detection requires that the process clock and system clock be set to calibrated timing. Idling is disabled by default.

The **DUMPDEV** and **DUMPCTL** options configure the set of jumpers on the rear of the CPU front panel that preset the device number and control value for the cold dump process. These values are used when the **DUMP** command is entered without the optional control/device number. The device number range is 0–127 decimal, and the control value range is 0–377 octal. The default control value corresponds to the Write Record tape command.

The **SET CPU STOP** command enables one or more simulation stop conditions. These are described in the *Simulation Stops* section below.

The **SET CPU EXEC** command configures instruction execution tracing. This command is described in the *Tracing* section below.

The CPU configuration may be displayed with the following commands:

| Command        | Action                                                |

|----------------|-------------------------------------------------------|

| SHOW CPU       | Display the device configuration                      |

| SHOW CPU STOPS | Display the enabled simulation stops                  |

| SHOW CPU EXEC  | Display the matching criteria for execution tracing   |

| SHOW CPU DUMP  | Display the cold dump device number and control value |

| SHOW CPU SPEED | Display the current simulation speed                  |

When the process clock is calibrated, the current simulation speed, expressed as a multiple of the speed of a real HP 3000 Series III, may be obtained with the **SHOW CPU SPEED** command. The speed reported will not be representative if the simulator was executing a PAUS instruction when it was stopped.

#### 3.1.1 System Halt

The MPE operating system is supported by special microcode features that perform code and data segment mapping, segment access bounds checking, privilege checking, etc. The layout of certain in-memory tables is

known to both the OS and the microcode and is used to validate execution of instructions. For instance, every stack instruction is checked for a valid access within the stack segment boundaries, which are set up by the OS before program dispatch. For this reason, the 3000 cannot be operated as a "bare" machine, because these tables will not have been initialized. Similarly, the cold load process by which the OS is loaded from storage media into memory is entirely in microcode, as machine instructions cannot be executed until the required tables are loaded into memory.

This OS/microcode integration means that the microcode may detect conditions that make continued execution impossible. An example would be an absent segment fault for the segment containing the disc I/O driver. If such a condition is detected, the CPU does a *system halt*. This fatal microcode error, distinct from a regular programmed halt, causes operation to cease until the CPU is reset.

A system halt stops the simulator and reports the system halt code to the simulation console. The code indicates the reason for the system halt, as follows:

| Code | Reason for System Halt                               |

|------|------------------------------------------------------|

| 1    | STT violation while executing in segment 1           |

| 2    | Absent code segment while executing on the ICS       |

| 3    | Code segment 1 is absent                             |

| 4    | Stack overflow while executing on the ICS            |

| 5    | I/O channel timeout                                  |

| 6    | I/O device timeout while executing IXIT or cold load |

| 7    | Cold load channel program checksum error             |

| 8    | Cold load channel program abort                      |

| 9    | Dispatcher already enabled while executing PSEB      |

| 12   | Cold load channel is not the system controller       |

| 13   | CST violation while executing in segment 1           |

| 17   | Cold load channel cannot become the controller       |

| 23   | External interrupts disabled while executing LOCK    |

| 33   | Attempt to trace segment 1                           |

If a system halt has occurred, simulator execution may not be resumed until a **RESET**, **RESET CPU**, or **LOAD** command has been entered.

#### 3.1.2 Idling

The PAUS instruction suspends instruction execution until an interrupt occurs. It is intended to defer instruction fetches from memory to allow full-bandwidth access by the Selector and Multiplexer Channels. If enabled, the simulator will idle only during execution of PAUS.

## 3.1.3 Simulation Stops

The simulator can be configured to detect certain machine instruction conditions and stop execution when one or more of them occur. Four stop options control the simulation stop conditions:

| Option | Stop Condition                                     |

|--------|----------------------------------------------------|

| LOOP   | Stop when an infinite loop is executed             |

| PAUSE  | Stop when a PAUS instruction is executed           |

| UNDEF  | Stop when an undefined instruction is executed     |

| UNIMPL | Stop when an unimplemented instruction is executed |

Setting the *LOOP* option stops the simulator if it attempts to execute an instruction that enters an infinite loop (e.g., BR P+0). The branch instructions TBA, TBX, BCC, BR, BCY, BNCY, BOV, and BNOV result in an infinite loop if the branch displacement is zero and the branch condition is true. The remaining branch instructions cannot result in an infinite loop, as they all modify the CPU state and so eventually will reach a point where they drop out of their loops.

Setting the **PAUSE** option stops the simulator if execution of a PAUS instruction is attempted. Setting the **UNDEF** option stops the simulator if execution of a non-canonical instruction (i.e., an instruction containing a decoded reserved bit pattern other than that defined in the *Machine Instruction Set* manual) is attempted. Setting the **UNIMPL** option stops the simulator if execution of an unimplemented instruction is attempted.

After a simulation stop, execution may be resumed in one of two ways. If the cause of the stop has not been remedied and the stop option has not been disabled, resuming execution with *CONTINUE*, *STEP*, *GO*, or *RUN* will cause the stop to occur again. Alternately, specifying the –*B* switch with any of the preceding commands will resume execution while bypassing the stop for the current instruction.

When the simulator examines the bit patterns of instructions to execute, each will fall into one of four categories:

- 1. Defined (canonical) instruction encodings, where all bits are defined or all reserved bits are zero (e.g., LOAD).

- 2. Undefined (non-canonical) instruction encodings, where reserved fields are "don't care" bits (e.g., MOVE).

- 3. Undefined (non-canonical) instruction encodings, where reserved fields are decoded (e.g., IXIT).

- 4. Unimplemented instruction encodings (e.g., stack opcode 072, or EADD without the EIS firmware option installed).

Instructions in categories 1 and 2 are always executed. The **UNDEF** option stops the simulator for instructions in category 3. The intent is to catch instructions containing reserved fields with values that change the meaning of those instructions. The **UNIMPL** option stops the simulator for instructions in category 4.

Bypassing a stop has the following effect:

| Option | Bypass Action                                           |

|--------|---------------------------------------------------------|

| LOOP   | Resume execution of the infinite loop                   |

| PAUSE  | Resume execution with the instruction following PAUS    |

| UNDEF  | Resume execution with decoding as in the hardware       |

| UNIMPL | Resume execution with an Unimplemented Instruction trap |

Note that the **PAUSE** action corresponds in hardware to pressing the HALT button and then the RUN button. If the stop conditions are disabled, the simulator performs the actions above, except that PAUS suspends instruction execution until a device interrupt occurs.

#### 3.1.4 Tracing

When debug output logging is enabled, tracing may be configured by specifying one or more of the reporting level options:

| Option | Reporting Level                         |

|--------|-----------------------------------------|

| INSTR  | Machine instructions executed           |

| DATA   | Memory data accesses                    |

| FETCH  | Memory instruction fetches              |

| REG    | Register values                         |

| OPND   | Memory operand values                   |

| EXEC   | Matching instruction execution states   |

| PSERV  | Process clock service events (periodic) |

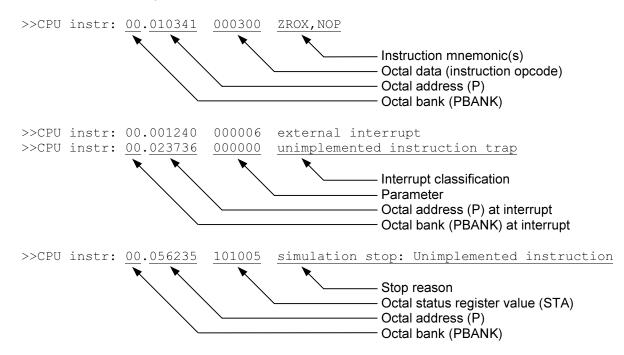

A section of an example trace is:

```

>>CPU fetch: 00.010342

020320

instruction fetch

>>CPU instr: 00.010341

000300 ZROX, NOP

>>CPU reg: 00.006500 000000

X 000000, MitrocCCG

>>CPU fetch: 00.010343 041100

instruction fetch

>>CPU instr: 00.010342 020320 PLDA

>>CPU data: 00.000000 001340 absolute read

>>CPU reg: 00.006500 000001

A 001340, X 000000, M i t r o c CCG

>>CPU fetch: 00.010344 037777

instruction fetch

>>CPU instr: 00.010343 041100 LOAD DB+100

>>CPU data: 00.002100 123003

data read

>>CPU

reg: 00.006500 000002

A 123003, B 001340, X 000000, M i t r o c CCL

>>CPU fetch: 00.010345 023404

instruction fetch

>>CPU instr: 00.010344 037777 ANDI 377

>>CPU req: 00.006500 000002 A 000003, B 001340, X 000000, Mitroc CCG

>>CPU fetch: 00.010346 002043

instruction fetch

>>CPU instr: 00.010345 023404 MPYI 4

>>CPU reg: 00.006500 000002

A 000014, B 001340, X 000000, M i t r o c CCG

>>CPU fetch: 00.010347 020320

instruction fetch

```

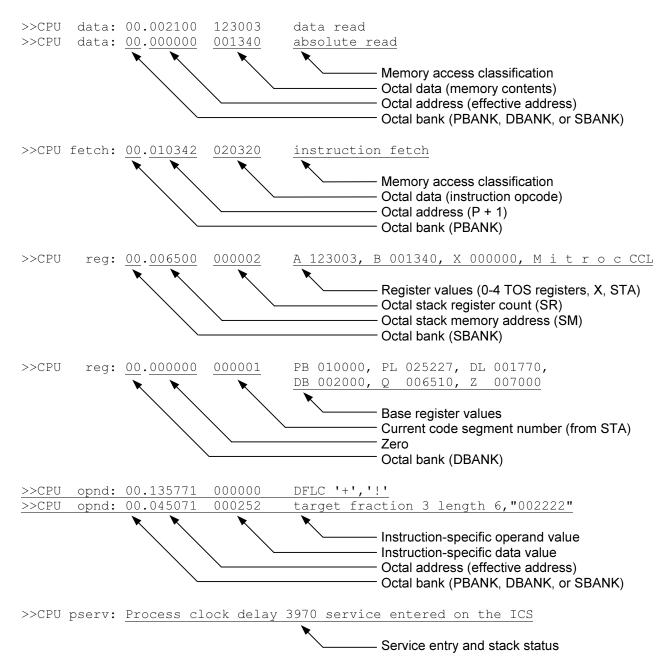

The *INSTR* option traces instruction executions. Each instruction is printed before it is executed. The two opcodes of a stack instruction are printed together before the left-hand opcode is executed. If the right-hand opcode is not NOP, it is reprinted before execution, with dashes replacing the just-executed left-hand opcode.

The *DATA* option traces reads from and writes to memory. Each access is classified by the memory bank register that is paired with the specified offset — DMA, absolute, program, data, or stack. DMA (channel) accesses derive their bank addresses from the banks specified by Set Bank I/O program orders. Absolute accesses always use bank 0. Program, data, and stack accesses use the bank addresses in the PBANK, DBANK, and SBANK registers, respectively.

The *FETCH* option traces instruction fetches from memory. These accesses are separated from those traced by the *DATA* option because fetches usually are of little interest except when debugging the fetch/execute sequence. Because the HP 3000 has a two-stage pipeline, fetches load the NIR (Next Instruction Register) with the instruction after the instruction about to be executed from the CIR (Current Instruction Register).

The *REG* option traces register values. Two sets of registers may be printed. After executing each instruction, the currently active TOS registers, the index register, and the status register are printed. After executing an instruction that may alter the base registers, the program, data, and stack segment base registers are printed.

The **OPND** option traces memory byte operand values. Some instructions take memory and register operands that are difficult to decode from **DATA** or **REG** traces. This option presents these operands in a higher-level format. The memory bank and address values are always those of the operands. The operand data and values printed are specific to the instruction. For example, the ALGN instruction prints its source and target operands, digit counts, and fraction counts, and the EDIT instruction displays its subprogram operations.

The *EXEC* option traces the execution of instructions that match user-specified criteria. When a match occurs, all of the above CPU trace options are turned on for the duration of the execution of the matched instruction. The prior trace settings are restored when a match fails. This option allows detailed tracing of specified instructions while minimizing the log file size compared to a full instruction trace.

The **SET CPU EXEC** command configures the match and mask values used to qualify instructions for execution tracing. Qualification is performed by ANDing the current instruction with the specified *mask* value and then comparing the result with the specified *match* value. If the *mask* value is omitted, the *match* value must match the instruction exactly. The values are entered in the CPU's data radix, which defaults to octal but may be set to a different radix or overridden by a switch on the command line.

Setting the *mask* value allows matching a range of instructions or an instruction with a range of operand values. For example, *SET CPU EXEC=020460;177760* will trace execution of all COBOL-II firmware instructions, *SET CPU EXEC=054000;077000* will trace execution of FDIV instructions, and *SET CPU EXEC=031000* will trace execution of PCAL 0 instructions. To trace a stack instruction, configure the match for the opcode in the left-hand position only; this will match the opcode in either position.

The **PSERV** option traces process clock event service entries. Each trace reports whether the CPU was executing on the Interrupt Control Stack or the user stack when the process clock ticked. Execution on the ICS implies that the operating system is executing. As the process clock ticks every millisecond, enabling **PSERV** tracing can quickly produce a large number of trace lines.

If one or more of the CPU trace options are in effect at the time that a simulation stop occurs, an instruction trace showing the stop reason will be included.

The trace formats are interpreted as follows:

For **OPND** traces of byte-array operands, the data values printed are the relative byte addresses. For EDIT subprogram operations, the value of the loop counter is printed.

Enabling CPU tracing can produce a very large number of lines very quickly, so care should be used to enable tracing only around the area of interest. Breakpoint actions may be used to implement this; for example:

BREAK 100; SET CPU DEBUG; GO BREAK 200; SET CPU NODEBUG; GO

These commands will enable tracing when the program counter reaches location 100 and disable tracing when it reaches location 200, thereby producing a trace of instructions executed between locations 100 and 200. Alternately, if the execution of specific instructions is of interest, the *EXEC* trace option may be used to reduce the debug log file size.

#### 3.1.5 Registers

| Name  | Size | Radix | Symbolic     | Read-Only    | Description                   |

|-------|------|-------|--------------|--------------|-------------------------------|

| CIR   | 16   | _     | $\checkmark$ | $\checkmark$ | Current Instruction Register  |

| NIR   | 16   | -     | $\checkmark$ | $\checkmark$ | Next Instruction Register     |

| PB    | 16   | 8     |              |              | Program Base Register         |

| Р     | 16   | 8     |              |              | Program Counter               |

| PL    | 16   | 8     |              |              | Program Limit Register        |

| PBANK | 4    | 8     |              |              | Program Segment Bank Register |

| DL    | 16   | 8     |              |              | Data Limit Register           |

| DB    | 16   | 8     |              |              | Data Base Register            |

| DBANK | 4    | 8     |              |              | Data Segment Bank Register    |

| Q     | 16   | 8     |              |              | Stack Marker Register         |

| SM    | 16   | 8     |              |              | Stack Memory Register         |

| SR    | 3    | 8     |              |              | Stack Register Counter        |

| Z     | 16   | 8     |              |              | Stack Limit Register          |

| SBANK | 4    | 8     |              |              | Stack Segment Bank Register   |

| RA    | 16   | 8     | $\checkmark$ |              | Top of Stack Register         |

| RB    | 16   | 8     | $\checkmark$ |              | Top of Stack – 1 Register     |

| RC    | 16   | 8     | $\checkmark$ |              | Top of Stack – 2 Register     |

| RD    | 16   | 8     | $\checkmark$ |              | Top of Stack – 3 Register     |

| X     | 16   | 8     | $\checkmark$ |              | Index Register                |

| STA   | 16   | _     | $\checkmark$ |              | Status Register               |

| SWCH  | 16   | 8     | $\checkmark$ |              | Switch Register               |

| CPX1  | 16   | 8     |              |              | Run-Mode Interrupts Register  |

| CPX2  | 16   | 8     |              |              | Halt-Mode Interrupts Register |

| PCLK  | 16   | 8     |              |              | Process Clock Register        |

The CPU state contains the registers visible to the programmer and the interrupt system control registers:

The CIR and NIR registers default to CPU instruction mnemonic format, and the STA register defaults to CPU status mnemonic format for display and entry but may be overridden with a numeric-format switch, if desired. The RA, RB, RC, RD, X, and SWCH registers may be examined or deposited using any of the modes described in the *Symbolic Display and Entry* section above.

Two additional, hidden, read-only registers may be displayed if mentioned explicitly. CNTR represents the hardware counter used by the microcode. When a PAUS or HALT instruction is executed, the microcode stores the value of the SR register in the CNTR register before flushing the TOS registers to memory (so SR is always zero after executing either instruction). The MOD register holds the module number during an unsolicited module interrupt. CNTR and MOD are provided for the CPU diagnostic and have no other use under simulation.

# 3.2 I/O Processor

The HP 30003B I/O Processor works in conjunction with the CPU and Multiplexer Channel to service the device interfaces. All I/O interfaces are connected to the IOP bus, which transfers direct I/O orders to the interfaces and handles memory reads and writes between the interfaces and the CPU stack. In addition, it provides the memory interface for Multiplexer Channel transfers, as well as fetching I/O program orders from main memory for the channel.

The IOP device has no configuration options. It does provide tracing, though, with selectable filtering by device number, using these device options:

| Option                   | Action                                          |

|--------------------------|-------------------------------------------------|

| FILTER= <list></list>    | Suppress tracing for device numbers in the list |

| NOFILTER                 | Enable tracing for all device numbers; default  |

| DEBUG= <option></option> | Enable tracing                                  |

| NODEBUG                  | Disable tracing; default                        |

Enabling IOP tracing can produce a very large number of trace lines very quickly, so care should be used to enable tracing only around the area of interest. If only certain devices are of interest, others may be filtered out of the results by specifying their device numbers in a *SET IOP FILTER* command. This command takes a list of individual device numbers separated by semicolons and ranges of the form *Iow-high*. For example, *SET IOP FILTER=3;7-9* would exclude lines pertaining to device numbers 3, 7, 8, and 9 from the trace report.

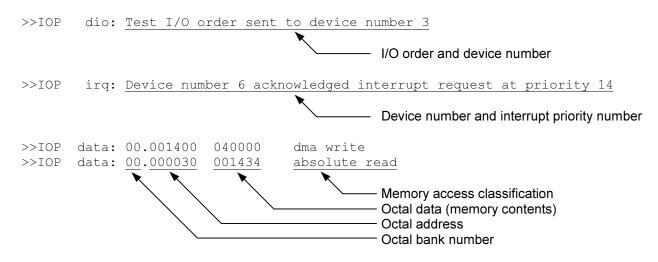

When debug output logging is enabled, tracing may be configured by specifying one or more of the reporting level options:

| Option | Reporting Level                          |

|--------|------------------------------------------|

| DIO    | Direct I/O orders issued                 |

| IRQ    | Interrupt requests received              |

| DATA   | Multiplexer Channel memory data accesses |

The *DIO* option traces direct I/O orders that are sent to devices. The *IRQ* option traces interrupt requests received and granted. The *DATA* option traces memory accesses performed on behalf of the Multiplexer Channel. Each access is classified as either an absolute access in memory bank 0 or a DMA access in the memory bank specified by a Set Bank I/O program order.

The trace formats are interpreted as follows:

The I/O Processor state contains these registers:

| Name | Size | Radix | Read-Only    | Description          |

|------|------|-------|--------------|----------------------|

| IOA  | 8    | 8     | $\checkmark$ | I/O Address Register |

## 3.3 Selector Channel

The HP 30030C Selector Channel provides high-speed data transfer between a device and main memory. While several interfaces may be connected to the selector channel bus, only one transfer is active at a time, and the channel remains dedicated to that interface until the transfer is complete. The channel contains its own memory port controller, so transfers to and from memory bypass the I/O Processor.

Once started by an SIO instruction, the channel executes I/O programs independently of the CPU. Program words are read, and device status is written back, directly via the port controller.

The SEL device has no configuration options. It does provide tracing, though, using these device options:

| Option                   | Action                   |

|--------------------------|--------------------------|

| DEBUG= <option></option> | Enable tracing           |

| NODEBUG                  | Disable tracing; default |

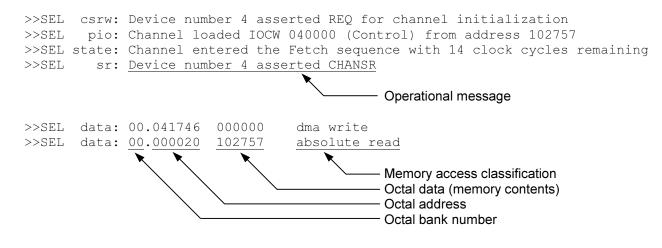

When debug output logging is enabled, tracing may be configured by specifying one or more of the reporting level options:

| Option | Reporting Level                             |

|--------|---------------------------------------------|

| CSRW   | Channel command initiations and completions |

| PIO    | Programmed I/O orders executed              |

| STATE  | Channel state changes executed              |

| SR     | Service requests received                   |

| DATA   | Channel memory data accesses                |